# **DETAILED PROJECT REPORT**

## On

# CHIPS TO STARTUP (C2S) PROGRAMME

Microelectronics Development Division R&D in Electronics Group Ministry of Electronics & Information Technology Government of India

सत्यमेव जयते

## Contents

| Preamble            |                                                                    | 3 |

|---------------------|--------------------------------------------------------------------|---|

| Background          | 4                                                                  | 4 |

| 2.0 Impact Assess   | ment Report on Special Manpower development Programme for Chips to |   |

| System Design       |                                                                    | 9 |

| 3.0 Evolving of Chi | ips to Startup Programme32                                         | 1 |

| 4.0 Chips to Start  | up (C2S) Programme                                                 | 2 |

| 4.1 Objectives.     |                                                                    | 2 |

| 4.2 Participatin    | g Institutions                                                     | 3 |

| 4.3 R&D Projec      | ts Deliverables and Outcomes3                                      | 3 |

| 5.0 Categories of F | Projects Funding - Criterion, Classification and Outcomes42        | 1 |

| 5.1 Criteria for Mo | nitoring Technology Readiness Level (TRL)42                        | 1 |

| 5.2 Project Categ   | orization44                                                        | 4 |

| 6.0 Programme Im    | aplementation                                                      | 9 |

| 6.1 Participatin    | g Institutions                                                     | 9 |

| 6.2.1 Project Imp   | lementation Unit (PIU)53                                           | 3 |

| 6.2.2 C2S Web Sit   | te                                                                 | 3 |

| 6.3 Monitoring      | and Review Mechanism                                               | 4 |

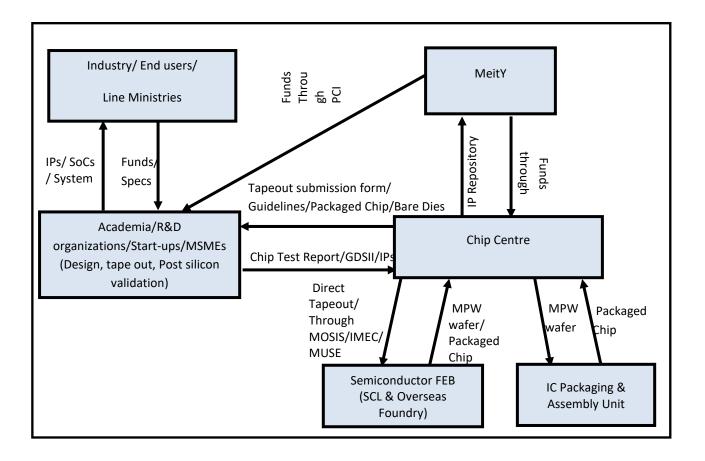

| 7.0 Chip Centre &   | Design Centre                                                      | 9 |

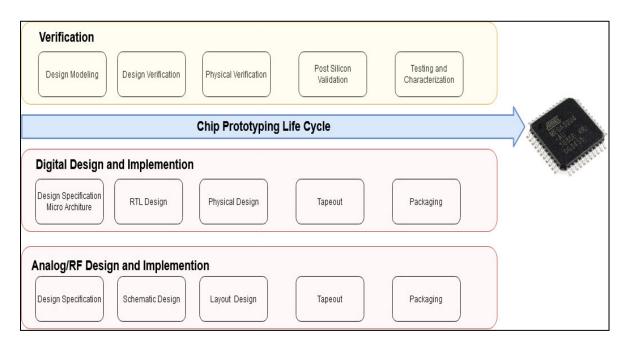

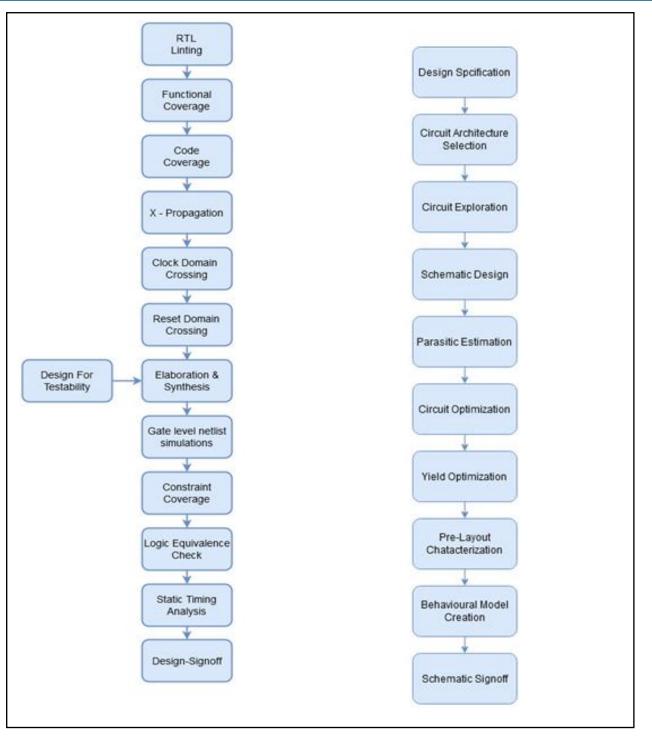

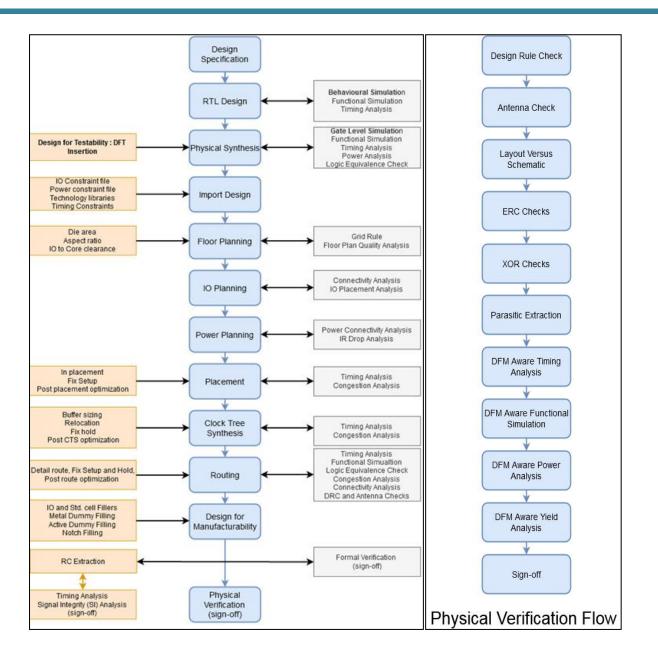

| 7.1 VLSI IC Desi    | ign Flow                                                           | 9 |

| 7.2 Upgradatio      | n of Chip Centre                                                   | 2 |

| 7.3 Establishme     | ent of Design Centre                                               | 5 |

| 7.4 Chip Centre ar  | nd Design Centre Budget Heads69                                    | 9 |

| 8.0 Financial Deta  | ils                                                                | D |

| PERT Chart of the ( | C2S activities to be undertaken                                    | 9 |

## Preamble

To position India as a global hub for Electronics System Design and Manufacturing (ESDM) by encouraging the driving capabilities in the Country, Ministry of Electronics and Information Technology has come out with National Policy on Electronics 2019 (NPE-2019) for developing core components including chipsets and creating an enabling environment for the industry to compete globally. One of the main objectives of National Policy on Electronics 2019 is to Strengthen and leverage the existing manufacturing, research, design and development hubs for promoting design and innovation in the field of Electronics by working closely with Government, Industry, Academia, Universities and other Institutions of learning to design programme ensuring availability of adequate skilled manpower to the industry.

VLSI Design activity is one of the key areas of Microelectronics. This activity is knowledge intensive as well as capital intensive as it requires relatively less investment as compared to other areas of Microelectronics which is capital intensive. The knowledge-based industry such as VLSI Design, Embedded Design etc. leverages the skills of professionals for its growth & expansion. The fastest growing Indian software sector also needs VLSI design and embedded design professionals for moving up the value chain necessary for both accelerating and maintaining the growth rate. National Policy on Electronics 2019 also emphasizes on creating a globally competitive Electronic Design and Manufacturing Industry to meet the Country's need and to serve the international market by focusing on skills, technology and scale. In order to fulfill the vision and mission of NPE-2019, there is a fundamental need to create highly skilled and trained manpower in the areas of VLSI design and Embedded system by developing IPs/ASICs/SoCs/Systems for targeted applications through collaborative projects with Academia/R&D Organizations/Startups/MSMEs/Industries.

Special Manpower Development Programme for Chips to System Design (SMDP-C2SD) has already inculcated the culture of development of Working Prototypes of SoCs/Systems /Sub-systems in the Academic / Research Institutes with identified Societal applications. To move up in the value chain and in order to fulfil the vision and mission of NPE-2019, there is a strong need to involve Industry(s) / Start-up(s) / MSMEs/ Incubate(s) / End user(s) (strategic / non-strategic) as part of SMDP Programme for design and development of users oriented, field trialled, deployable and re-usable IPs / SoCs / ASICs / Systems in addition to Specialized Manpower generation for Industry.

The proposed umbrella Programme "Chips to Startup (C2S)" not only aims at generating specialized manpower in the area of VLSI Design and Embedded System but also inculcating the culture of entrepreneurship in related areas by way of facilitating translational research in collaboration with Industry/Start-ups etc.

## Background

## 1.1 Initiation of SMDP Phase-I

During the 9th Plan, MeitY had initiated the project entitled "Special Manpower **Development Programme in VLSI Design and Related Software (SMDP-I)**" in Year 1998 with a view to increase India's share of the Global VLSI Design market from 0.5% to 5% by end of the 9th Plan period by making available specialized manpower required by the Design Centers / Industry. (SMDP- Phase-I) was implemented at 19 Academic and Research Institutions categorised into Resource Centres (7 in number - 5 IITs, IISc, CEERI) and Participating Institutes (12 in number) with a total outlay of Rs. 14.99 Crores. This programme resulted in generating about 9300 trained personnel with hands-on experience in VLSI design and related areas.

The following were the main activities undertaken during the Phase-I of the Special Manpower Development programme in VLSI Design and related Software:

- **i. Instruction Enhancement Programme-**These programmes were for the faculty of Participating Institutions in selected topics of Microelectronics and related areas. The Programmes were typically of one week duration.

- **ii. Training Laboratory Technicians** –The aim of this activity was to train the laboratory technicians on the hardware and software tools given under the program to the institutions so that they can be efficiently installed and effectively used by the students of the institutes.

- **iii.** Setting up of VLSI Design Laboratories-VLSI Designing is one of the most important activities of Microelectronics. To promote Microelectronics in the country efforts had to be made to bring out the 'VLSI Design' culture in the country. It was with this view that Design Laboratories were set up with Electronic Design Automation (EDA) tools for design of VLSI circuits and appropriate hardware. These labs thus became the 'Fabless Design Centres' where the students could design the circuits.

- iv. Development of Learning Material (LMs) on various topics of VLSI and related software – The main aim of this activity was to make available quality learning material on core subjects of Microelectronics / VLSI Design to faculty and students of the participating institutions.

- v. Teaching of various courses on VLSI Design and related software at:

- ➤ B.Tech /B.E. Level (Type-IV Manpower)

- M.E. / M.Tech level in areas of Electronics, Communications, Computer Science, Instrumentation etc. (Type-III Manpower)

- M.E. / M.Tech in VLSI Design and Microelectronics (Type-II Manpower)

PhD on different aspects of VLSI Design and Related Software (Type-I Manpower)

The aim here was to offer Microelectronics / VLSI courses to the students of institutes so that they could take up design projects / carry out research in this area.

## 1.2 Continuation of Programme in Tenth Plan: Initiation of SMDP Phase-II

The Phase II of the **Special Manpower Development Programme in VLSI design and related software (SMDP II)** was initiated in 2005 during the 10<sup>th</sup> Plan as a continuation of Phase I with the aim of consolidating the efforts that were made during the 9<sup>th</sup> Plan for generation of trained manpower required for VLSI design. The Phase II of the SMDP project brought additional participating institutions under its purview making the total number of implementing organisations to 32 with total outlay of Rs. 49.98 Crores and duration of 5 years which was later extended by three more years. Under SMDP-II, a total of 28,170 engineering graduates in Electronics/ Communication/ Computer Science/ Instrumentation etc. had taken a graduate level course in VLSI design. At post graduate level, 6,439 students had taken at least two courses in various aspects of VLSI Design and CAD. An additional 3,924 post graduate students had their specialization at ME/M. Tech in VLSI design & CAD. Further 402 PhDs in various aspects of VLSI design & CAD were enrolled/ generated.

The following were the objectives of the programme:

- Primary Objective -To train special manpower in the area of VLSI Design and related software at M.E./M.Tech level (Type-II manpower). In addition to this, generation of Type-III manpower i.e. M.E./M.Tech in other areas of electronics etc. with at least two courses on VLSI design will also be undertaken.

- Secondary Objective To train Type-IV manpower i.e. B.E/B. Tech in Electronics etc. with graduate level courses on VLSI Design. However, the program will not only be limited to generation of Type-II, III & IV manpower but would endeavour to generate PhD in various aspects of VLSI design/microelectronics (Type-I manpower) manpower as well. The establishment of VLSI design laboratories at all the 32 intuitions would also strengthen their academic program.

## 1.2.1 Major elements of the Programme were

- i. Establishing State -of-the art VLSI Design Laboratory.

- ii. Generation of manpower in VLSI Design area at various levels.

- iii. Instruction Enhancement Program (IEP) for Faculty of PIs.

- iv. Workshop involving International Guest Faculty.

- v. India Chip Program.

- vi. National VLSI website and 7 sites at RCs.

| Date of Initiation: | 21.03.2005      |

|---------------------|-----------------|

| Date of Completion: | 31.03. 2013     |

| Total Outlay        | Rs.49.98 Crores |

## 1.2.2 Implementing Institutions

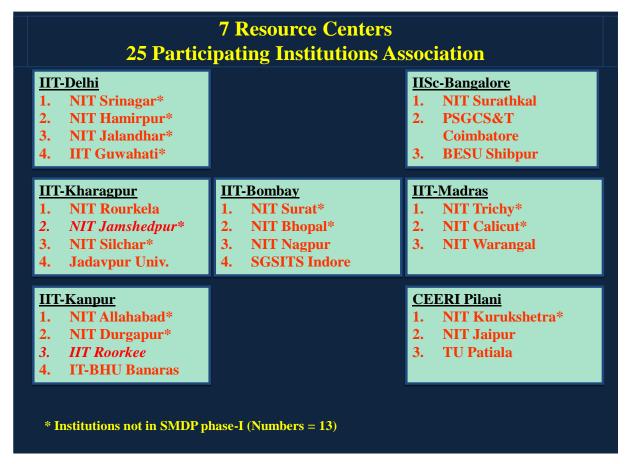

7 Resource Centres (including 5 IITs, IISc Bangalore and CEERI Pilani) and 25 Participating Institutes (including 17 NITs and 8 other Institutions). The 32 institutions that supported as Resource Centres & Participating Institutions in Special Manpower Development Programme for VLSI Design and Related Software (Phase-II) are listed below in Table 1.1.

#### **Table 1.1: Institutions under SMDP Phase-II**

## 1.2.3 Achievements against Major Elements of the Programme

## 1.2.3.1 Establishing State-of-the art VLSI Design Laboratory

VLSI Design Laboratories were established at 32 institutions equipped with State-of-the-art Hardware platforms and Electronic Design Automation (EDA) Tools. These Labs were being used by students at various levels (B.Tech / M.Tech / PhD) to undertake design of VLSI circuits. The details of the Hardware and EDA Tools are given in the Table 1.2 below.

|                       |            | At RCs                |             |

|-----------------------|------------|-----------------------|-------------|

| Hardware Details      | Quantity   | EDA Tools             | Licenses    |

| High end PC Servers   | 6 Nos      | Cadence Tools Bundle  | 10 licenses |

| PC P4 based           | 14 Nos     | Synopsys Tools Bundle | 5 licenses  |

| Printer, Scanner      | 1 No. each | Magma Tools Bundle    | 10 licenses |

| Associated networking |            | Mentor Tools Bundle   | 50 licenses |

| UPS – 15 KVA          | 1 Nos.     | CoWare Tools          | 5 licenses  |

|                       |            | Xilinx                |             |

|                       |            | At PIs                |             |

| Hardware Details      | Quantity   | EDA Tools             | Licenses    |

| High end PC Servers   | 3 Nos      | Cadence Tools Bundle  | 10 licenses |

| PC (P4 based)         | 9 Nos      | Synopsys Tools Bundle | 5 licenses  |

| Printer               | 1 No.      | Magma Tools Bundle    | 5 licenses  |

| Associated networking |            | Mentor Tools Bundle   | 50 licenses |

| UPS – 15 KVA          | 1 No.      | CoWare Tools          | 5 licenses  |

|                       |            | Xilinx                |             |

## Table 1.2: Hardware and EDA Tools

## 1.2.3.2 Generation of manpower in VLSI Design area at various levels

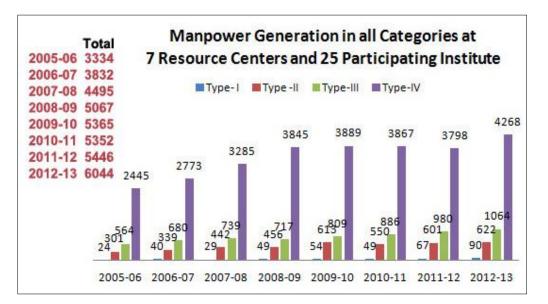

Under the Programme, the students of RCs and PIs at various levels such as B.Tech, M.Tech and Ph.D where introduced to specialized topics in VLSI Design. A model curriculum was also developed and adopted by the Institutions. The primary target of the Programme was to generate substantial number of manpower at M.Tech level having VLSI design as their primary specialization. B.Tech level as well as M.Tech Students in other areas also undertook courses (as electives) in VLSI and Microelectronics. The manpower generated under this programme at various levels is depicted in the Table 1.3 and in Fig. 1.1 below:

| Academic<br>Year                                                                | 2005-06 | 2006-07 | 2007-08 | 2008-09 | 2009-10 | 2010-11 | 2011-12 | 2012-13 | Total |

|---------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

| Type- I                                                                         | 24      | 40      | 29      | 49      | 54      | 49      | 67      | 90      | 402   |

| Type -II                                                                        | 301     | 339     | 442     | 456     | 613     | 550     | 601     | 622     | 3924  |

| Type-III                                                                        | 564     | 680     | 739     | 717     | 809     | 886     | 980     | 1064    | 6439  |

| Type-IV                                                                         | 2445    | 2773    | 3285    | 3845    | 3889    | 3867    | 3798    | 4268    | 28170 |

| Total                                                                           | 3334    | 3832    | 4495    | 5067    | 5365    | 5352    | 5446    | 6044    |       |

| Type-I: PhD. Type-II:ME/M.Tech (VLSI), Type-III: ME/M.Tech, Type-IV: BE/B.Tech. |         |         |         |         |         |         |         |         |       |

**Table 1.3: Generated Manpower**

Fig. 1.1: Types of Manpower Generated

## **1.2.3.3 Instruction Enhancement Program (IEP) for faculties of PIs**

23 Instruction Enhancement Programmes (IEPs) on different topics/areas were conducted at various RC/PI locations by Resource Centres for training faculty of Participating Institutions. A total of 654 faculties/Lab Engineers of PIs were trained through this programme. Details of various IEPs conducted are listed in the Table 1.4 below.

| #   | Торіс                                                               | Name of the<br>Institute | Date                 | No. of<br>participants<br>attended |

|-----|---------------------------------------------------------------------|--------------------------|----------------------|------------------------------------|

| 1.  | Digital IC Design                                                   | IIT Kanpur               | July 3-14, 2006      | 21                                 |

| 2.  | Low Power VLSI Design                                               | IIT Kharagpur            | Sep. 11-23, 2006     | 24                                 |

| 3.  | RF IC Design                                                        | IIT Madras               | Nov. 13-24, 2006     | 27                                 |

| 4.  | Semiconductor Device<br>Modelling& Simulation                       | IISc Bangalore           | Dec. 4-15, 2006      | 18                                 |

| 5.  | Analog IC Design                                                    | IIT Delhi                | July 2-13, 2007      | 27                                 |

| 6.  | VLSI-DSP Based Design                                               | IIT Kharagpur            | Sep. 24-Oct 05, 2007 | 27                                 |

| 7.  | Synthesis of Digital System                                         | IIT Kanpur               | Dec. 10-21, 2007     | 25                                 |

| 8.  | VLSI Testing & Verification                                         | IISc Bangalore           | Mar. 10-19,2008      | 24                                 |

| 9.  | Technology CAD                                                      | IIT Kharagpur            | May 12-17,2008       | 11                                 |

| 10. | Linux System Administration<br>and EDA Tools Installation           | CEERI Pilani             | Oct. 14-18, 2008     | 26                                 |

| 11. | Mixed-Signal VLSI Design                                            | IIT-Bombay               | March 16-21, 2009    | 33                                 |

| 12. | FPGA Laboratory                                                     | IIT Delhi                | July 13-18,2009      | 15                                 |

| 13. | System Modeling Using<br>System C/VHDL/Verilog                      | CEERI Pilani             | Dec. 14-23,2009      | 17                                 |

| 14. | Algorithms to Architectures                                         | IIT Madras               | Feb. 22-26,2010      | 17                                 |

| 15. | Low-Power, High Speed<br>Digital Subsystem Design :<br>Spec to Test | IIT Kharagpur            | March 2-13,2010      | 14                                 |

| <b>Table 1.4:</b> | Various IEPs | conducted | and | number | of | participants |

|-------------------|--------------|-----------|-----|--------|----|--------------|

|                   |              | comaccea  |     |        |    | pur norpunos |

| 16. | Chip Integration and Tape out | IIT Madras        | Sept.29-Oct.2nd,2010                  | 27  |

|-----|-------------------------------|-------------------|---------------------------------------|-----|

|     | Issues                        |                   |                                       |     |

| 17. | Semiconductor Memory          | CEERI Pilani      | Dec.13-17, 2010                       | 52  |

|     | Design & Test                 |                   |                                       |     |

| 18  | VLSI aspects on Biomedical    | IIT Kharagpur     | March 06-12,2011                      | 22  |

|     | Engineering                   |                   |                                       |     |

| 19. | Low Noise Low Power OP        | IIT Delhi         | March $14^{th} - 19^{th}$ , 2011      | 25  |

|     | Amp Design and Testing        |                   |                                       |     |

| 20. | India Chip: Chip finishing    | IIT Bombay        | Oct. $8^{th} - 10^{th}$ ,2011         | 25  |

|     | workshop                      |                   | ,                                     |     |

| 21. | Analog/Mixed Signal Design    | IIT Madras, IISc. | Dec. $9^{th} - 12^{th}$ ,2011         | ~60 |

|     |                               | Bangalore IIT     | · · · · · · · · · · · · · · · · · · · |     |

|     |                               | Delhi             |                                       |     |

| 22. | RFIC & System Design          | IIT Delhi         | Jan 20, 2012                          | ~20 |

| 23. | Low Power Digital Design      | IIT Kanpur        | Sept. 24-28, 2012                     | 21  |

## 1.2.3.4 India Chip Program

Fabrication of fourteen chips, 5 in single mode and 9 in "Multi Project Wafer (MPW)" mode were undertaken for Siliconization of Analog and Digital designs done by students of various RCs and PIs. In the five single mode design - IIT D prototyped 2 individuals designs whereas each of IIT M, IIT G and IIT Kharagpur prototyped single designs. For the design undertaken by IIT Kharagpur sub blocks were designed by NIT Durgapur, Jadavpur University and IIT Kharagpur itself.

In the MPW chips, 32 designs from 16 institutions were integrated together and were prototyped in nine chips. Seven institutions merged these 32 designs in 9 chips for Siliconization which acted like an integrator to merge the designs received from other institutions. In this way there was considerable savings in the fabrication cost. The institutions, which carried out the integration/merging of designs were, IISc Bangalore, IIT Guwahati, NIT Tiruchirapalli, IIT Kanpur, NIT Surathkal, VNIT Nagpur and IIT Kharagpur.

In addition to this, one MPW design was also carried out by IIEST Shibpur which had integrated designs from IIT Kharagpur, NIT Rourkela and IIEST Shibpur. This design was fabricated at Euro practice. Another MPW integrating designs obtained from MANIT Bhopal, MNNIT Allahabad, NIT Hamirpur, MNIT Jaipur, NIT Jalandhar, NIT Kurukshetra, NIT Silchar, CEERI Pilani were integrated by MeitY and submitted for fabrication at Euro practice by CEERI Pilani. The packaged chips received after fabrications were tested by the respective institutions. The details of all the MPW designs undertaken are shown in Table 1.5 below.

| Mixed Signal Design from IIT | Analog & Digital Design:     | Analog Design from IIT Delhi | Analog & Digital                  |          |

|------------------------------|------------------------------|------------------------------|-----------------------------------|----------|

| Madras                       | Integrating Design from      |                              | Design from IIT                   |          |

|                              | four institutions            |                              | Guwahati                          |          |

|                              |                              |                              |                                   |          |

| Digital Design: Integrating  | Analog Design from           | Analog Design: Integrating   | Analog Design:                    |          |

| designs from 5 institutions  | IIT-Delhi                    | designs from 2 institutions  | Integrating designs from          | om       |

|                              |                              |                              | 3 institutions                    |          |

| NIT THEN INTASYCON           |                              |                              |                                   |          |

| Digital Design: Integrating  | Analog Design: Integrating   | Analog & Digital Design      | Analog & Digital Des              | ign:     |

| designs from 2 institutions  | designs from 6 institutions  | from IIT-Kgp                 | Integrating designs from          | om       |

|                              |                              |                              | three institutions.               |          |

|                              | BESU Shibpur<br>NIT Rourkela |                              | MNNIT Allahabad,<br>MANIT Bhopal, | Design   |

|                              | IIT Kharagpur                |                              | CEERI Pilani,<br>DEITY Delhi,     | 1-Bit A  |

|                              |                              |                              | NIT Hamirpur,<br>MNIT Jaipur,     | 6-BIT I  |

|                              |                              |                              | NIT Jalandhar,                    | 10-Bit : |

|                              |                              | ADC,Key board decoder        | NIT Kurukshetra,                  | 4 4 1    |

| Transistor Level S-Box       |                              | circuit for microcontroller  | NIT Silchar                       | 4x4 key  |

| Design for Efficient         |                              | interface, Adder, Hamming    |                                   |          |

| Implementation of the AES IC |                              | Code Decoder, Differential   |                                   |          |

| Implementation of Control    |                              | amplifier, Parity Generator  |                                   |          |

| Area Network (CAN) ADC.      |                              | d designs under India Chi    |                                   |          |

Table 1.5: Chip Layout views of integrated designs under India Chip Programme

## 1.2.3.5 Workshop involving International Guest Faculty

The workshops on Recent Advances in Analog VLSI Design; Technology and Application of Medical Imaging; VLSI Interconnects & Signal Integrity; and Cognitive Radio and CMOS RF Circuit and System challenges were organized at various RC locations during January 11-18, 2007, January 03-16, 2011, November 25-December 15, 2011 and January 09-20, 2012 respectively. In these workshops, Prof. W.A Serdijn, from Technical University Delft Netherlands, Dr. Rajiv Gupta from Massachusetts General Hospital/Harvard Medical School, Prof. Ram Achar from Carleton University, Ottawa, Ontario and Prof. Eric Klumperink from University of Twente were invited to give series of lectures on the current area of research. The details of the workshops is given in table 1.6 below.

| Name of Invited  | Period      | Торіс                                             | Location        |

|------------------|-------------|---------------------------------------------------|-----------------|

| Guest Faculty    |             |                                                   |                 |

| Prof. Wouter A.  | January 11- | Recent Advances in Low- Power, Low Voltage Analog | IIT Kharagpur   |

| Serdijn Delft    | 18,2007     | Designs and Ultra –wide band Transceivers         | IIT Delhi       |

| University       |             |                                                   | IIT Madras      |

| Dr. Rajiv Gupta. | January 03- | Technology and Application of Medical Imaging     | IIT Kharagpur   |

| Harvard Medical  | 16, 2010    |                                                   | IIT Delhi       |

| School           |             |                                                   | IIT Bombay      |

|                  |             |                                                   | CEERI + BITS    |

| Prof. Ram        | November    | Fundamental & Advances in VLSI Interconnects &    | IIT Delhi       |

| Achar.           | 25 -        | Signal Integrity                                  | CEERI Pilani    |

| Carleton         | December    |                                                   | IIT Kharagpur   |

| University       | 15,2011     |                                                   | IIT Bombay      |

|                  |             |                                                   | IISc. Bangalore |

|                  |             |                                                   | NIT Surathkal   |

|                  |             |                                                   | PSGCT           |

|                  |             |                                                   | Coimbatore      |

| Prof. Eric       | January     | Cognitive Radio and CMOS RF Circuit and           | IISc. Bangalore |

| Klumperink       | 09-20,      | System challenges.                                | IIT Madras      |

| University of    | 2012        | Wideband Receivers exploiting thermal Noise       | IIT Bombay      |

| Twente           |             | Canceling.                                        | IIT Delhi       |

|                  |             | Advances in low jitter CMOS clock generation.     |                 |

|                  |             | CMOS Frequency Translation Circuits               |                 |

## **Table 1.6: Workshops Conducted**

## 1.2.3.6 National VLSI website and 7 sites at RCs

The seven Resource Centres had established individual websites to disseminate information connected with VLSI design. A centralized website (http://www.smdp2vlsi.gov.in ) was also established at DeitY which acted as a repository of all information and facilitated its access to institutions which were not covered under SMDP-II. The model curriculum developed, lecture materials for all the IEPs held were made available through this website. The URL of the website created for SMDP-II by various centres is given below.

- IIT Bombay: http://www.ee.iitb.ac.in/~smdp/

- IIT Madras: http://www.ee.iitm.ac.in/vlsi/start

- IIT Kanpur: http://www.iitk.ac.in/vlsi/

- IIT Kharagpur: http://www.smdp.iitkgp.ernet.in/

- IISc. Bangalore: http://www.cedt.iisc.ernet.in/smdp/

- CEERI Pilani: http://idg.ceeri.ernet.in/smdp2.html

- IIT Delhi: http://web.iitd.ac.in/~ee/~iec/smdp.html

## 1.2.3.7 Other Activities Undertaken in SMDP-II

i. "Best M.Tech Thesis Award" was awarded to RCs & PIs during the three consecutive years (2007-08, 2008-09, and 2009-10). The details of these are given in the table 1.7 below.

|                    | Resource Centres                                                                                                 |

|--------------------|------------------------------------------------------------------------------------------------------------------|

| FY 2007-08         | First Prize: "Adaptive Keeper Design for Dynamic Logic Circuits Using<br>Rate Sensing Technique" IISc. Bangalore |

|                    | Second Prize : "Design of an Analog VLSI Chip to emulate Directional an                                          |

|                    | d Orientation Selectivity in Visual Cortex" IIT Delhi                                                            |

| FY 2008-09         | First Prize: "Low Power Design Techniques for the Front End of a Radio                                           |

|                    | Frequency Communication Receiver" IISc. Bangalore                                                                |

|                    | Second Prize: "FPGA based Video Tracker" IIT Kharagpur                                                           |

| FY 2009-10         | First Prize (Joint Award):1. "Non-Quasi Static Modelling of Multi-Gate                                           |

|                    | MOSFETs" IISc. Bangalore.                                                                                        |

|                    | 2. "Power and Performance Optimization Using Multi Voltage, Multi                                                |

|                    | Threshold and Clock Gating" IIT Kanpur                                                                           |

| Participating Inst | litutes                                                                                                          |

| FY 2007-08         | First Prize: "Design and Analysis of 12 Bit Segmented DAC" Thapar                                                |

|                    | University                                                                                                       |

|                    | Second Prize: "Design, Modelling & Simulation of MEMS Capacitive Shunt                                           |

|                    | Switch and its Application as Phase Shifter for Ku Band" Jadavpur                                                |

|                    | University                                                                                                       |

| FY 2008-09         | First Prize: "Design of Resolution Adaptive TIQ Flash ADC using AMS                                              |

|                    | 0.35-micron Technology" NIT Surathkal                                                                            |

|                    | Second Prize: "Design of Multi-band CMOS Low Noise Amplifier" IIT                                                |

|                    | Guwahati                                                                                                         |

| FY 2009-10         | First Prize: "VLSI Architecture of Galois Field Arithmetic Circuit" IIEST                                        |

|                    | Shibpur                                                                                                          |

|                    | Second Prize: "Design of a 0.5 V Low Power Analog Front-End for Heart-                                           |

|                    | rate Detector" IIT Guwahati                                                                                      |

#### Table 1.7: Best M.Tech Thesis awards under the programme

ii. Financial support was provided to attend 20 International conferences to Institutions participating in the SMDP-II project. The Table 1.8 given below summaries the support provided to various institutions.

| Name of the RC                                                          | Name of the PI                                                                                                                                                              | Name of Conference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IIT Kanpur -3<br>IIT Kharagpur -1<br>CEERI Pilani – 1<br>IIT Madras - 1 | NIT Trichy - 2<br>NIT Calicut - 3<br>PSG - Coimbatore - 1<br>Thapar University Patiala<br>- 1<br>MNIT Jaipur - 1<br>NIT Srinagar - 1<br>SGSIT Indore - 3<br>IIT Roorkee – 2 | IEEE International conference on Field<br>Programmable Technology , ICED – 2008 , 24 <sup>th</sup> IEEE<br>Norchip Conference , 24 <sup>th</sup> IEEE Norchip Conference ,<br>IEEE ISCAS – 2006 , ICIIS -2007 , International<br>Conference on Materials for Advanced Technologies<br>2007 , IMOC – 2007 , ISCAS – 2008, DATICS –<br>2009, IEEE IMEC-DATICS-2009, ICCS-<br>2008,WCESCS 2008, TENCON-2009, IEEE<br>computer Society Annual Symposium, IEEE<br>Symposium on Computer and Informatics (ISCI<br>2011), IEEE International Conference on Electronic<br>Devices, Systems & Applications (ICEDSA 2011),<br>AUTOTESTCON 2011, IEEE NATW 2012 Woburn<br>USA,ISCAS Seoul, Korea. |

## Table 1.8: Support provided to attend International conferences

## 1.3 Continuation of Programme in Eleventh Plan: Initiation of SMDP-C2SD

During the 11<sup>th</sup> Plan, as a continuation of II Phase, 3<sup>rd</sup> Phase of the Special Manpower Development Programme (SMDP III) was conceptualized by MeitY with an aim not only to develop specialized manpower in VLSI Design but also to develop Working Prototype of System-on-Chip/ System/Sub-Systems using the ASICs/ICs developed in-house.

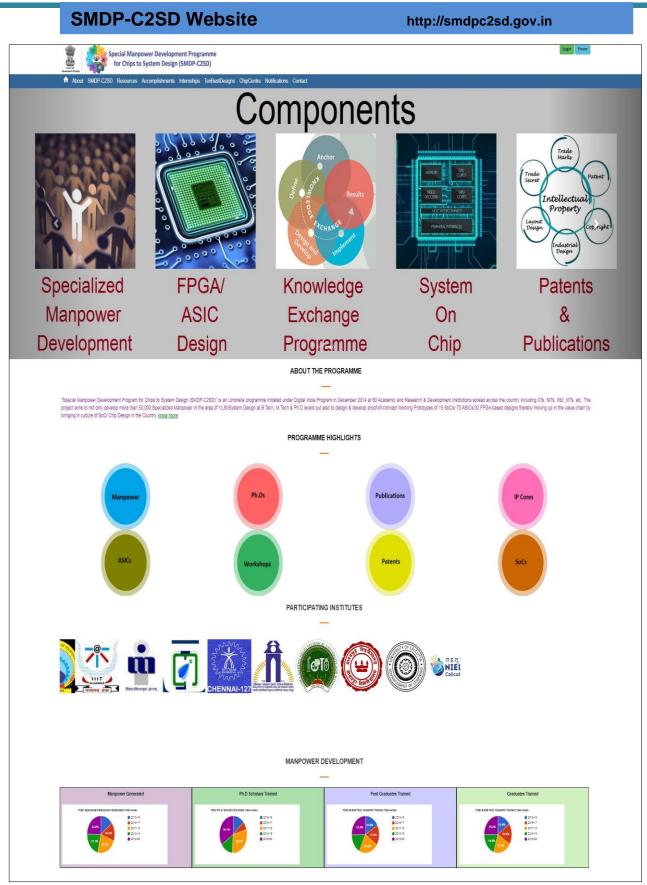

An umbrella Programme entitled "Special Manpower Development Programme for Chips to System Design (SMDP-C2SD)" was initiated under 'Digital India Programme' in December 2014 over a period of 5 years with total outlay of Rs. 99.72 Crore at 60 academic/ R&D institutions spread across the Country including IITs, NITs, IISc, IIITs & other Engineering Colleges with an aim to train 50,000 number of specialized manpower in the area of VLSI design and inculcate the culture of System-on-Chip (SoC)/ System Level Design at Bachelors, Masters and Research level. The Programme duration was later extended by 23 Months up to November, 2021.

The following were the objectives of the Special Manpower Development Programme for Chips to System Design:

- To bring in a culture of System on Chip / System designing by developing working prototypes with societal applications

- Capacity building in the area of VLSI/ microelectronics and Chip to System development.

- To broaden the base of ASIC / IC designing in the country

- To broaden the R&D base of Microelectronics / Chip to System through Networked PhD program

- To promote 'Knowledge Exchange Program'

- Protection of Intellectual Property generated

Date of Initiation: December 2014

Total Outlay: Rs. 99.72 Crore

**Duration:** 30<sup>th</sup> November 2021.

#### **Implementing Institutions**

The program is being implemented at 60 Institutions (including IITs, NITs, IISc, IIITs & other Engineering Colleges) spread across the country. There are 10 Resource Centres (RCs) which are the mentoring institutions for 50 Participating Institutions (PIs). The 60 Institutions participating in the program are listed below in Table 1.9.

| Category I          | Category II                                    | Category III                   |

|---------------------|------------------------------------------------|--------------------------------|

| 10 Resource Centres | Participating Institutions which were there in | New Participating Institutions |

|                     | SMDP-II and New IITs(which were not            | (20)                           |

|                     | earlier in SMDP-II) (30)                       |                                |

| 1. IIT Kharagpur    | PIs which were there in SMDP-II                | 41. NIT Agartala               |

| 2. IIT Bombay       | 11. NIT Srinagar                               | 42. NIT Patna                  |

| 3. IIT Madras       | 12. DBRANIT Jalandhar                          | 43. NIT Raipur                 |

| 4. IIT Kanpur       | 13. NIT Hamirpur                               | 44. NIT Sikkim                 |

| 5. IIT Delhi        | 14. NIT Kurukshetra                            | 45. NIT Goa                    |

| 6. IIT Guwahati     | 15. ThaparUniversity Patiala                   | 46. NIT Arunachal Pradesh      |

| 7. IIT Roorkee      | 16. MNIT Jaipur                                | 47. NIT Meghalaya              |

| 8. IISc Bangalore   | 17. MNNIT Allahabad                            | 48. NIT Nagaland               |

| 9. CEERI, Pilani    | 18. IIT(BHU) Varanasi                          | 49. NIT Manipur                |

| 10. VNIT, Nagpur    | 19. NIT Durgapur                               | 50. NIT Mizoram                |

|                     | 20. NIT Silchar                                | 51. NIT Uttarakhand            |

|                     | 21. IIEST Shibpur                              | 52. NIT Delhi                  |

|                     | 22. PSG College of Technology, Coimbatore      | 53. NIT Puducherry             |

|                     | 23. NIT Jamshedpur                             | 54. IIIT Allahabad             |

|                     | 24. NIT Rourkela                               | 55. ABVIIITM Gwalior           |

|                     | 25. NIT Warangal                               | 56. PDPMIIIT(D&M) Jabalpur     |

|                     | 26. NIT Surathkal                              | 57. IIIT(D&M) Kanchipuram      |

|                     | 27. SVNIT Surat                                | 58. NIELIT Calicut             |

|                     | 28. MANIT Bhopal                               | 59. University of Calcutta     |

|                     | 29. SGSITS Indore                              | 60. Indira Gandhi Technical    |

|                     | 30. NIT Calicut                                | University for Women,          |

|                     | 31. NIT Tiruchirappalli                        | Delhi                          |

|                     | 32. Jadavpur University                        |                                |

|                     | New IITs                                       |                                |

|                     | 33. IIT Mandi                                  |                                |

|                     | 34. IIT Ropar                                  |                                |

|                     | 35. IIT Jodhpur                                |                                |

|                     | 36. IIT Bhubaneshwar                           |                                |

|                     | 37. IIT Gandhinagar                            |                                |

|                     | 38. IIT Indore                                 |                                |

|                     | 39. IIT Hyderabad                              |                                |

|                     | 40. IIT Patna                                  |                                |

|                     | TV. 111 1 aula                                 |                                |

#### Table 1.9: Institutions under SMDP-C2SD

## 1.3.1 Achievements against Major Elements of the SMDP-C2SD Programme

# 1.3.1.1 Development of Specialized Manpower in VLSI / SoC / System / Sub-System Designing

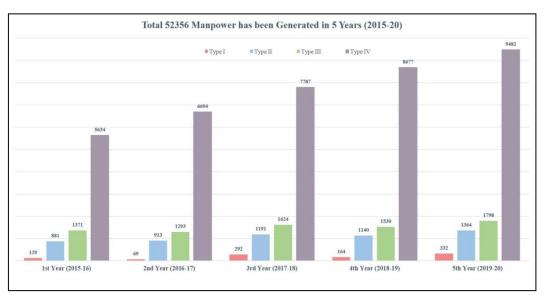

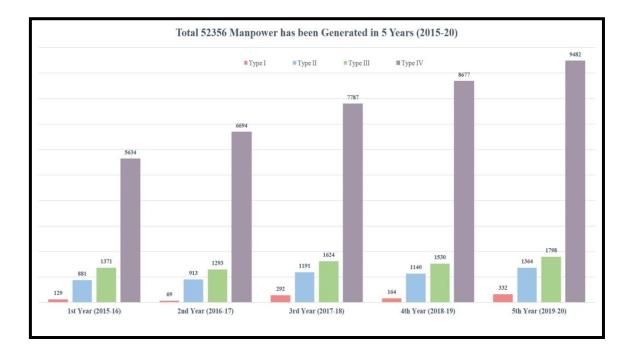

Under the programme, during first 5 Year of Programme, 52,365 no. of Industry ready Specialised Manpower has been generated in VLSI/ System Design Area at B.Tech, M.Tech and PhD level, which includes:

- Type-I (PhD)

- Type-II (M.Tech in VLSI),

- Type-III (M.Tech in Computer/ Communication etc. with at least two VLSI courses / minor project in VLSI)

- Type-IV (B.Tech with at least two VLSI Courses/ minor project in VLSI)

And other Students, who have utilized the VLSI Lab Resources created at Institutions under SMDP Programme.

The manpower generated under this programme at various levels is depicted in the Table 1.10 and in Fig. 1.2 below:

Fig. 1.2: Types of Manpower generated

| #        | 1st Year<br>(2015-16) | 2nd Year<br>(2016-17) | 3rd Year<br>(2017-18) | 4th Year<br>(2018-19) | 5th Year<br>(2019-20) | Total |

|----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|

| Type I   | 129                   | 69                    | 292                   | 164                   | 332                   | 986   |

| Type II  | 881                   | 913                   | 1191                  | 1140                  | 1364                  | 5419  |

| Type III | 1371                  | 1293                  | 1624                  | 1530                  | 1798                  | 7556  |

| Type IV  | 5634                  | 6694                  | 7787                  | 8677                  | 9482                  | 38082 |

| Total    | 8015                  | 8969                  | 10894                 | 11511                 | 12976                 | 52365 |

Table 1.10: No of Manpower Generated

#### 1.3.1.2 Establishing State–of-the art VLSI Design Laboratory

State-of-the-Art VLSI Design Laboratories were established at 60 Institutions equipped with Hardware platforms and Electronic Design Automation (EDA) Tools from Cadence/ Synopsys/ Mentor/ Xilinx. These labs are not only used by students involved under SMDP-C2SD project to undertake design of VLSI circuits but also by students from other Departments & nearby institutes.

#### **1.3.1.3 Development of Working Prototype of Systems**

Under the programme, in order to inculcate the culture of Chip to System development activity at Institutions, 15 Systems/SoCs were undertaken by 10 RCs for development of Working Prototype. For each system project, End users were identified and specifications were finalized in consultation with them. The End users were also involved in the Project Review Committee for continuous monitoring of the Project. Systems developed under the Programme are listed below.

| #  | System Project Title                                                                                     | RC      | End User/ Application                    |  |  |

|----|----------------------------------------------------------------------------------------------------------|---------|------------------------------------------|--|--|

| 1  | ASIC for Next Generation LCA                                                                             | IISc-B  | ADA (DRDO) & ISRO                        |  |  |

| 2  | Integrated microchip module for wireless capsule endoscopy                                               | IIT-D   | Healthcare                               |  |  |

| 3  | Collision Detection in Automobiles using CMOS Imagers                                                    |         | Healthcare                               |  |  |

| 4. | MAVI: Mobility Assistant for the Visually Impaired                                                       |         | Automotive                               |  |  |

| 5. | Versatile Data Acquisition & Signal Processing Platform<br>with specific emphasis on Seismic Application | IIT-Kgp | Disaster Management, MoES                |  |  |

| 6. | Design and Implementation of variable data rate (up to 10 GBPS) (SerDes Serializer/ Deserializer) system |         | ISRO and DRDO                            |  |  |

| 7  | Wireless Sensor Networks Node for Internet of Things (IoT)                                               | VNIT-N  | Railways                                 |  |  |

| 8  | Versatile Physiological Signal Monitoring System                                                         | IIT-B   | Healthcare                               |  |  |

| 9  | SerDes: High Speed Data Transceiver                                                                      |         | SAC (ISRO)                               |  |  |

| 10 | Low Power Speech Recognition System using a custom IC                                                    | IIT-M   | Consumer Electronics                     |  |  |

| 11 | UWB beam-forming Camera                                                                                  |         | Strategic                                |  |  |

| 12 | Wireless Sensor Node – System On Chip (WSN-SOC) for<br>Monitoring of illegal activities                  | IIT-K   | Forest Department of Odisha              |  |  |

| 13 | RF Sensing of Cardiopulmonary Motion for survival detection under debris                                 | IIT-R   | NDRF Uttarakhand/ Disaster<br>Management |  |  |

| 14 | System-on-Chip platform for Secured Speech Communication                                                 | CEERI   | Strategic sector                         |  |  |

| 15 | FPGA/ASIC based Sensor Platform for Monitoring Air Pollutants                                            | IIT-G   | Assam Pollution Control<br>Board         |  |  |

#### Table 1.11: System Developed under the Programme

## **System Projects**

Versatile Data Acquisition & Signal Processing Platform with specific emphasis on Seismic Application is being designed by IIT Kharagpur. This system can generate the early warning within one second of P-Wave to save lives and property beyond 200 KM from the earth quake epicenter. After testing and field trials, the whole system will be deployed in earth quake detection centre installed at Sikkim funded by Ministry of Earth Science, Government of India.

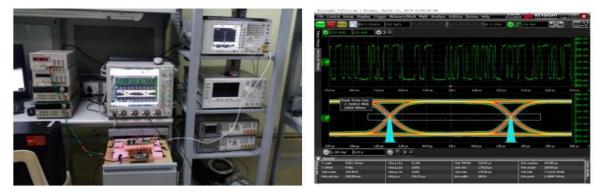

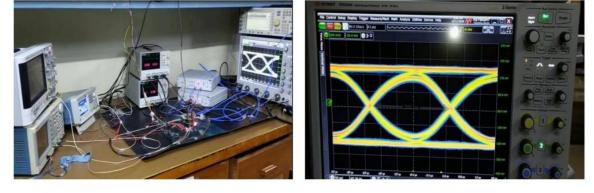

2 IIT Kharagpur has also developed Serializer Deserializer (SerDes) with data rate of 12.5 Gbps. The design is being explored by ISRO for usage in Satellite Launch vehicles and further enhancements as per their requirements. IITKGP is also in process of designing a SerDes with 20 Gbps data rate.

5

## **System Projects**

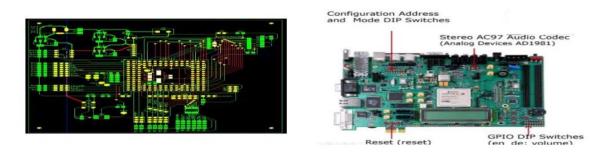

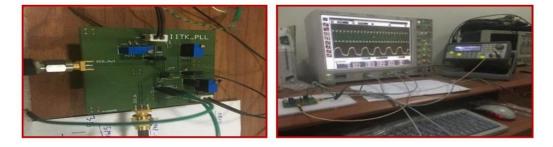

The design, development and implementation of an open-source IP core based system-on-chip (SOC) design platform and its application to Secure Speech Transmission & Reception is in process by CEERI Pilani for Centre for Artificial Intelligence and Robotics (CAIR), DRDO. The sub-modules of the system like Vocoder, Cipher etc. are developed by CEERI in-house.

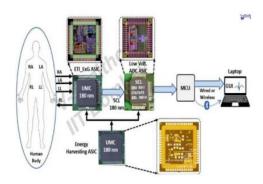

4 **IISc Bangalore** is developing a mixed signal ASIC for smart probe for Next Generation LCA. A Working prototype has been developed for Wireless Telemetry System with Energy Harvesting for Strategic Sectors: Probe for LCA (DRDO), Satellite Wiring Harness (ISRO), Launch Vehicle telemetry (ISRO). Close interaction with ADA, DRDO is in progress for incorporating their requirement in the System.

**A Versatile Physiological Signal Monitoring System for Healthcare** is being developed by **IIT Bombay**. A working Prototype has been developed for Versatile Physiological Signal Monitoring System using adaptive Artefact removal techniques.

## **System Projects**

6 A Serializer Deserializer with high-speed serial links for module-to-module or chip-to-chip communication on board satellites is also being developed by IIT Bombay. SerDes with data rate of 16 GBPS has been designed and interaction with ISRO is in progress.

Ĩ

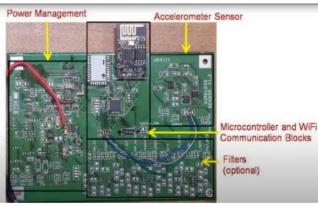

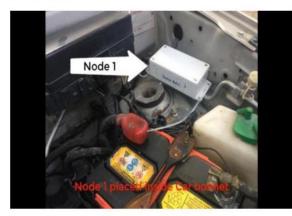

The design and development of Wireless Sensor Node at board level (COTS) and chip level with ZigBee standards is being developed by VNIT Nagpur for the use in Railways. A working prototype has been developed for WSN for Railway Stock Health Monitoring System. Field trials on the passenger train in Nagpur-Ramtek and on car with improved antenna characteristic have been conducted.

ĨO

A system for RF Sensing of Cardiopulmonary Motion for survival detection under debris is being developed by IIT Roorkee with an aim to detect humans trapped under debris in disaster affected areas using RF sensing of cardiopulmonary motion. The system will be later adopted by National Disaster Response Board (NDRF) Uttarakhand, National Disaster Management Authority, Govt. of Uttarakhand.

(9) An **On-chip Speech Recognition System** is being designed by **IIT Madras** with an aim to develop a standalone system for offline speech recognition with large language models with a primary interest as IP for embedded applications/SoCs.

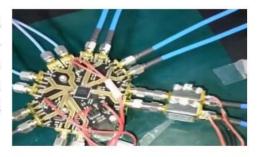

**10** The design and development of an **Array Signal Processor ASIC** is being carried out by **IIT Madras** which will be used by Naval Physical and Oceanographic Laboratory (NPOL) DRDO, Kochi.

11

12

## **System Projects**

An Air Quality Monitoring System (AQMS) is being developed by IIT Guwahati which can sense harmful gases like CO<sub>2</sub>, CO, NO<sub>2</sub> along with Temperature and Humidity sensing. Assam Pollution Control Board has been approached to adopt the system.

Wireless Sensor Node - System On Chip (WSN-SOC) for efficient sensing and monitoring of illegal activities such as Poaching and wood cutting in forest is being developed by IIT Kanpur and a

working prototype has been developed for Gun-shot and Wood-cutting sound detection. The field trials have been carried out in the forests of Orissa. The system will be adopted by the Forest Department, Govt. of Orissa.

13 IIT Delhi is designing an integrated microchip module for Wireless Capsule Endoscopy for Healthcare users. This system is a complete imaging solution (a prototype solution, on a single chip) for transmission of compressed digestive tract images over a wireless link

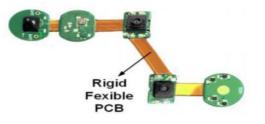

Figure 1: Fabricated sensor and test boards

## Ċ

## **System Projects**

A collision detector for detection of obstacles and collision in Automobiles using CMOS Imagers is being developed by IIT Delhi. A Working prototype has been developed for Collision Detection using CMOS Imagers for parallel velocity/depth estimation, motion direction classification, and robustness to background light. Interest has been received from automotive industry to incorporate their requirement.

15 **IIT Delhi** is also developing a system on **Mobility Assistant for Visually Impaired (MAVI)**. It is a device to aid mobility of visually impaired people and address the issues of safety (identify- digging, potholes and stray animals), navigation (guided movements) and social inclusion (Face detection and recognition). The system is capable of detecting and alerting presence of Dogs and Cows, Human faces + face recognition from a library, Signboards (English and/or Hindi) + reading them out. A Mobile App has been developed for the same.

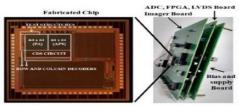

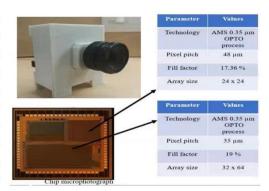

# **1.3.1.4** Development of Applications Specific Integrated Circuits (ASICs) and board level designs using FPGAs

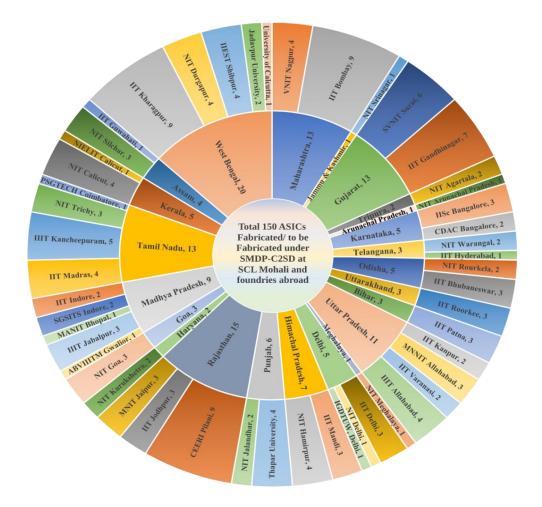

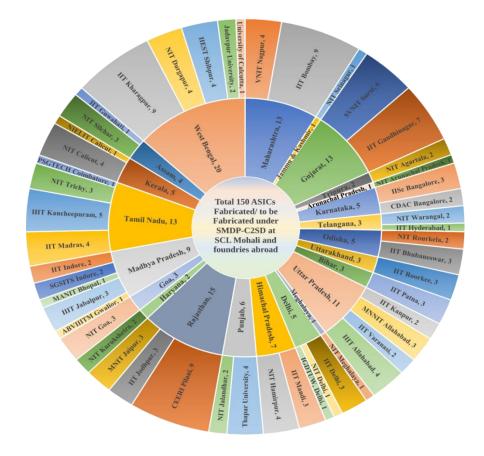

To provide the exposure of complete design cycle of Chip development, ASICs designs were also undertaken by Participating Institutions who were part of previous SMDP programmes. Some of the ASICs designed by the PIs were also used in the 15 Working Prototype SoCs/ Systems, being developed for Strategic & Societal sectors.Under the Programme, total 150 ASIC fabricated and being fabricated at SCL and outside foundry as depicted in Figure 1.3 below. Additionally, 30 FPGA based board level designs were also undertaken by Category III institutions.

Fig. 1.3: Total ASIC fabricated at SCL and outside foundry

## 1.3.1.5 Establishment of Chip Centre

For undertaking Siliconization of ASICs/Integrated Circuits designed by the Participating Institution, Chip Centre was established at C-DAC, Bangalore. Chip Centre is the nodal centre for integrating the designs received from Institutions and sending them for fabrication at SCL in MPW mode. Chip Centre also facilitated the Institutions for packaging of bare dies received from SCL. Under the Programme, through Chip Centre, 111 ASICs were fabricated

and being fabricated at SCL in MPW mode. Chip Centre has also prepared the Checklists and templates to streamline the process of chip tape out at participating Institutions.

## 1.3.1.6 India Chip Programme

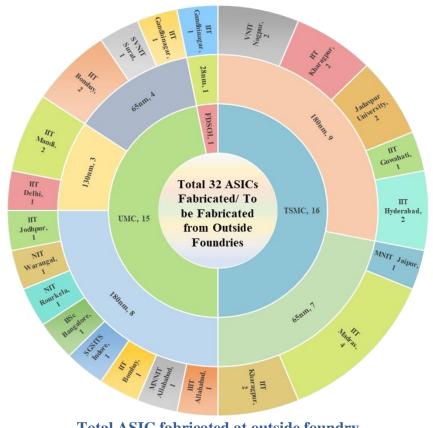

Under India Chip programme, ASICs fabricated by the Participating Institutions were supported for fabrication at overseas foundries in different technology nodes. Under India Chip Programme, total 32 designs were fabricated at outside foundry as depicted in Figure-1.4.

Fig. 1.4: Total ASIC fabricated at outside foundry

Also, for providing fabrication support to Institutions who were not the part of SMDP-C2SD programme, Request for Proposal announced at MeitY and SMDP-C2SD website for selecting 10 best designs per year for fabrication at SCL Mohali.

## **1.3.1.7 Instruction Enhancement Program (IEP) to enhance faculty expertise in** Microelectronics & Chip to System

Under the programme, 15 Instruction Enhancement Programme (IEPs) on different topics/area were conducted at various RC/PI locations by RCs and PIs for training faculty of Participating Institutions. A total of 1885 faculties/Lab Engineers of PIs were trained through this IEP. Details of various IEPs conducted are listed in the Table 1.12 below:

| #   | Institute                       | Date                      | Торіс                                                                 | Faculty/Student<br>Attended |

|-----|---------------------------------|---------------------------|-----------------------------------------------------------------------|-----------------------------|

| 1.  | IIT-D                           | 7- 9 Dec' 15              | System Level Design on Platform FPGAs                                 | 27                          |

| 2.  | IISc-B                          | 4- 8 Jul' 16              | Mixed Signal SOC: from design to tape<br>out (.GDS2)                  | 47                          |

| 3.  | IIT-B                           | 11- 13 Jul' 16            | Analog, Mixed-Signal and RF System<br>Design                          | 35                          |

| 4.  | VNIT-N                          | 5- 9 Dec' 16              | Design issues related to Deep Sub-Micron<br>Technologies              | 35                          |

| 5.  | IIT-KGP/ IIT-<br>Guwahati       | 10-14 Apr'17              | Introduction to Analog & Digital VLSI<br>Design                       | 22                          |

| 6.  | IIT-KGP/ NIT-<br>Sikkim         | 5-9 Jun' 17               | Mixed Signal and RFIC Design                                          | 27                          |

| 7.  | IIT Madras                      | 29Jan - 2 Feb' 18         | Analog IC Design                                                      | 25                          |

| 8.  | IIT Roorkee (with SCL Mohali)   | 24 - 29 Feb' 18           | High Level Design to Silicon                                          | 60                          |

| 9.  | IIT Kharagpur                   | 19- 23 Mar'18             | IoT for Structural Health Monitoring                                  | 30                          |

| 10. | CDAC Bangalore<br>(Chip Centre) | 10-14 June'19             | PCB Design methodologies - a hands-on course                          | 28                          |

| 11. | IISc Bangalore                  | 24-28 June'19             | Mixed Signal SoC: from tape out to GDSII                              | 49                          |

| 12. | NIT Rourkela                    | 1-5 <sup>th</sup> July 19 | Design Verification and Hardware Security                             | 18                          |

| 13. | IIEST Shibpur                   | 26-3 0 Aug 19             | Testing and Design-for-Testability for<br>Digital Integrated Circuits | 32                          |

| 14. | NIELIT Calicut                  | 05-16 Oct 2020            | Embedded System Design on FPGA covering Swadeshi Microprocessors      | 1000                        |

| 15. | (Online training)               | 30 Nov- 12 Dec 2020       | Embedded System Design on FPGA covering Swadeshi Microprocessors      | 450                         |

## Table 1.12: Conducted IEPs and number of participants

## **1.3.1.8** Support for International Conference/Workshop outside

Under the programme, Researchers/Students of the 12 Participating institutions were supported for attending International Conferences and to present their work. Apart from this, 6 International Conference/Workshops were also supported in the area of VLSI/System under the programme.

Additionally, 5 ZoPP Workshop were conducted yearly for- reviewing the Project activities carried out by Institutions and working out Annual Action plan for all project implementing institutions & preparing Project Planning Matrix (PPM) for measuring the performance of the institutions.

| #  | Institute Name               | Conference Name                                                                                                   | Year | Country            | Duration                                        |  |

|----|------------------------------|-------------------------------------------------------------------------------------------------------------------|------|--------------------|-------------------------------------------------|--|

| 1  | IIT Gandhinagar              | Radiation and its Effects on Components and Systems (RADECS)                                                      | 2016 | Germany            | 19 <sup>th</sup> -23 <sup>th</sup><br>September |  |

| 2  | IIT Hyderabad                | International Workshop on Signal Processing<br>Systems(SiPS)                                                      | 2017 | Lorient,<br>France | 2 <sup>nd</sup> -<br>5 <sup>th</sup> October    |  |

| 3  | Thapar<br>University,Patiala | International Conference on Electrical and Electronics Engineering (ICEEE)                                        | 2017 | Australia          | 2 <sup>nd</sup> -3 <sup>rd</sup><br>February    |  |

| 4  | CEERI Pilani                 | International System-on-Chip Conference                                                                           | 2018 | USA                | 4 <sup>th</sup> -7 <sup>th</sup><br>September   |  |

| 5  | IIT-Bombay                   | International Symposium on Circuits and Systems (ISCAS)                                                           | 2018 | Florence,<br>Italy | 27 <sup>th</sup> - 30 <sup>th</sup><br>May      |  |

| 6  | IIT Mandi                    | International Symposium on Circuits and Systems (ISCAS)                                                           | 2018 | ITALY              | 27 <sup>th</sup> -30 <sup>th</sup> May          |  |

| 7  | IIT-Guwahati                 | International Microwave Symposium (IMS)                                                                           | 2019 | Boston, USA        | 2 <sup>nd</sup> -7 <sup>th</sup> June           |  |

| 8  | IIT-Bombay                   | International Symposium on Circuits & Systems (ISCAS)                                                             | 2019 | Japan              | 26 <sup>th</sup> -29 <sup>th</sup> May          |  |

| 9  | Thapar<br>University,Patiala | International Conference on Intelligent Systems (Intellisys)                                                      | 2019 | UK                 | 5 <sup>th</sup> -6 <sup>th</sup><br>September   |  |

| 10 | IIEST Shibpur                | International Symposium on Devices, Circuits and Systems (ISDCS)                                                  |      | Japan              | $6^{\text{th}}$ -8 <sup>th</sup> March          |  |

| 11 | NIT Patna                    | International Symposium on Wireless Per<br>sonal Multimedia Communication (WPMC-2019)                             |      | Portugal           | $24^{th} - 27^{th}$<br>November                 |  |

| 12 | CEERI Pilani                 | International conference on trust privacy and<br>security in Intelligent System and Application<br>(IEEE TPS-ISA) | 2019 | California         | 12 <sup>th</sup> – 14 <sup>th</sup><br>December |  |

## Table 1.13: Support for attending International Conferences outside the Country

## Table 1.14: Support for Organizing International Conferences/Workshops in the Country

| # | Institute Name      | Conference Name                                  | Year | Duration                                   |

|---|---------------------|--------------------------------------------------|------|--------------------------------------------|

| 1 | IIT Roorkee         | International Symposium on VLSI Design and       | 2017 | $29^{\text{th}}$ -2 <sup>nd</sup> July     |

|   |                     | Test (VDAT)                                      |      |                                            |

| 2 | C-DAC Bangalore     | Analog VLSI & Mixed Signal Design                | 2017 | $15^{\text{th}}$ - $16^{\text{th}}$ June   |

| 3 | Thiagarajar College | International Symposium on VLSI Design and       | 2018 | $28^{\text{th}}$ - $30^{\text{th}}$ June   |

|   | of Engineering,     | Test (VDAT)                                      |      |                                            |

|   | Madurai             |                                                  |      |                                            |

| 4 | IIT Indore          | International Symposium on VLSI Design and       | 2019 | $4^{\text{th}}$ - $6^{\text{th}}$ July     |

|   |                     | Test (VDAT)                                      |      |                                            |

| 5 | IIT Goa             | ARM Architecture and System-on-Chip (SoC)        | 2019 | $1^{\text{st}}$ - $3^{\text{rd}}$ December |

|   |                     | Design                                           |      |                                            |

| 6 | IIEST Shibpur       | International Symposium on Devices, Circuits and | 2020 | $4^{th} - 6^{th}$ January                  |

|   |                     | System (ISDCS-2020)                              |      |                                            |

#### **1.3.1.9 Patens/Publications**

Under the Programme, 21 Patents have been filed by Participating Institutions in the area of VLSI/system design and about 1500 research papers published in reputed Conference Proceedings / Journals.

# 1.3.1.10 Developmentof Model Syllabus for B.Tech / M.Tech oriented towards SoC / System Designing and initiating M.Tech in VLSI / Embedded System Designing

With a view to promote System Designing in the country, a model syllabus / curriculum for B.Tech / M.Tech oriented towards SoC/ System Designing including practical works / minor projects etc. was prepared. The faculty of Resource Centres and other experts including experts from the industry was involved to work out the Model Syllabus. Efforts were made for adoption of this model syllabus curriculum oriented towards SoC / System Design in various institutions with the approval of their competent authorities which had facilitated the initiation of M.Tech in Microelectronics/VLSI design at 18 new participation institutions.

#### 1.3.1.11 Involvement of Industry Associations and Experts

To ensure that the program deliverables meet the industry requirement, the industry experts involved at all the stages of the program. The experts were made members of the National Steering Committee (NSC), Technical Advisory Committee (TAC) and Project Review and Steering Group (PRSG). Also, experts from the industry were also involved in identification of SoC / system under the sub-activity 'Chip to System Development'. Whereas students from SMDP-C2SD institutions sent to leading Semiconductor MNCs (Intel/ NXP/ Cadence/Synopsys & S.T.Microelectronics) for Internship of 6 months to 1 year duration throughout the programme.

## 1.3.1.12 Website Development and Web based dissemination of Educational Material

Under the programme, SMDP-C2SD website was developed by CDAC Delhi & being used to disseminate information including educational materials generated through IEP, Short-term courses, training programme on EDA tools, Review meeting, Information about Patent registered, Interactive forums to discuss design issues among researchers from 60 PIs.

The SMDP model of MeitY has been a successful model for targeted manpower development in a niche area. The program has successfully inculcated the culture of System-on-Chip/ System Development using mostly in-house designed ASICs / ICs at Academic institutions along with generation of expertise.

Enhancing the quality of the faculty through IEPs, Workshops etc. would have a long term positive impact on generation of quality manpower in the high technology VLSI Design and System Development

## 2.0 Impact Assessment Report on Special Manpower development Programme for Chips to System Design

Third-party review and evaluation of the SMDP-C2SD Program was conducted by **VLSI Society of India**. For review of Programme activities, several interactions were held between VLSI Society of India, IESA, Participating Institutions and MeitY. Various Programme activity of Programme were analysed and reviewed based on the information available at SMDP-C2SD website <u>http://smdpc2sd.gov.in/</u>.

Based on the objectives and goals of the SMDP-C2SD, assessment across 12 different categories is presented in the following Matrix.

| Goal                                                        | Target | Achieved          | Grade   | Comments                                                                                                                                        |

|-------------------------------------------------------------|--------|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Manpower<br>Development                                     | 50000  | 100%              | А       | Quality of the students could be better. Higher % of students in Type-I and Type-II should be targeted.                                         |

| VLSI Design<br>Laboratories                                 | 60     | 100%              | А       | Remote & Cloud based access to the infrastructure for Ease of access and better utilization of resources                                        |

| Development of<br>working prototype<br>systems              | 15     | 15                | В       | Technical content and Commercialization potential could be<br>improved by increasing effective industry participation.                          |

| ASIC and Board<br>Level Designs<br>Using FPGAs              | 30     | Goals<br>Achieved | В       | Tape-Outs could have better and diverse technical &research contents to cater to wider range of applications                                    |

| Establishment of<br>Chip Center                             |        | Goals<br>Achieved | B+      | Turn-around time for Tape-Outs was long and should be improved.                                                                                 |

| India Chip Program                                          |        | Goals<br>Achieved | B+      | More Tape-Outs at Advanced Nodes as per need of the application.                                                                                |

| Instruction<br>Enhancement<br>Program (Faculty<br>Training) | 15     | Goals<br>Achieved | В       | Need more work; Trained and capable faculty is the key to success                                                                               |

| International<br>Conference<br>Support                      |        | Goals<br>Achieved | В       | Bring and Support More International Conference in India.<br>Increase student and faculty participation in international<br>conferences abroad. |

| Patents and<br>Publications<br>(National,<br>International) |        | Goals<br>Achieved | А       | H-Index and Citation Index need significant improvement.                                                                                        |

| M. Tech & B. Tech<br>Model Syllabus                         |        | Goals<br>Achieved | В       | Need AICTE approved B.Tech Program in Electronics & VLSI                                                                                        |

| Industry and<br>Experts<br>Involvement                      |        | Goals<br>Achieved | В       | Quality and Quantity of Industry and Global Experts needs improvement                                                                           |

| Website<br>Development                                      |        | Goals<br>Achieved | А       | Good Start, Let's device a way to collate all knowledge generated in a systematic manner.                                                       |

| <b>Overall Score</b>                                        |        |                   | 8.83/10 |                                                                                                                                                 |

VLSI Society of India has made the following recommendations in respect of future roadmap to broaden & strengthen the base of VLSI design in the country:

- (i) **Broaden & strengthen the base of VLSI/ Chip design in the country** by way of including new/ more institutions in next phase of SMDP.

- (ii) **Optimal utilization of design infrastructure** to be made in next phase of SMDP by way of making efforts towards cloud based access of EDA Tool license and Compute/ storage infrastructure.

- (iii) Streamlined process for design tape out at foreign foundries to be worked out by working out advance agreements with demand aggregators (viz. IMEC, Euro practise, e-FAB etc), packaging & board design service providers. Provide opportunities for SMDP-C2SD students/ researchers to undergo research internship at leading fabs.

- (iv) Focus on faculty development by way of implementing collaborating programmes with industry wherein faculty to spend working at industry and vice-versa. International conferences of repute may be activity supported / organized under SMDP-C2SD.

- (v) Focus on generating Industry-ready manpower by way of initiating new bachelor's programme in Electronics and VLSI design, providing internship opportunities to students/ researchers.

- (vi) More number of Academia-industry collaborative projects to be supported for translation of technology by way of regular reviews and identifying/ supporting projects having commercialization potential / part-funding from industry (preferably).

- (vii) Translation of technology to be encouraged by way of supporting projects focusing on national priorities, part-funding (preferably) from industry and creating linkages with other schemes (i.e. proposed F-DLI (Fabless design linked incentive) Scheme, NIDHI/PRAYAS programme and TBI etc).

The detailed Assessment report is placed at Annexure A

## 3.0 Evolving of Chips to Startup Programme

India's share in the global hardware electronics production is about 3% and the share of domestic electronics production in India's GDP is 2.3%. In 2017-18, the import of electronic goods was of the order of USD 53 billion (approximately INR 3, 44,500 crore) which is expected to rise rapidly to about USD 400 billion (approximately INR 26, 00,000 crore) by 2025 (*Source: NPE 2019*). With an aim to reduce the import of electronics product and to promote the domestic manufacturing and export in the entire value-chain of ESDM, National Policy on Electronics (NPE)-2019 was formulated to drive the capabilities in the Country by developing core components, including chipsets, core and peripheral IPs, creating an enabling environment for the Industry to compete globally and to Provide support for significantly enhancing the availability of skilled manpower in the ESDM sector.

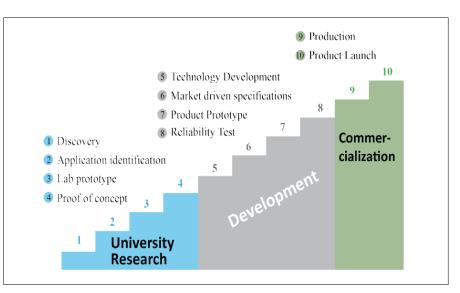

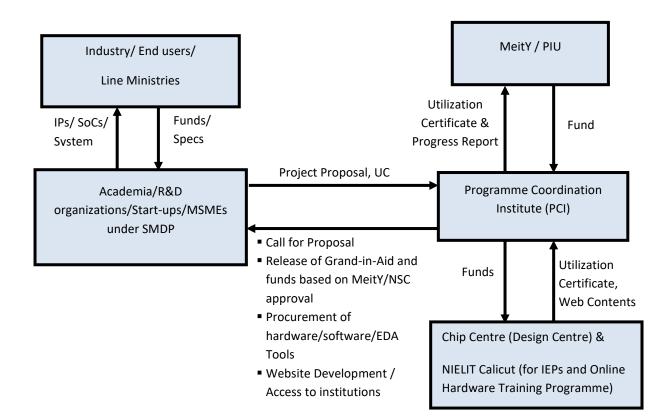

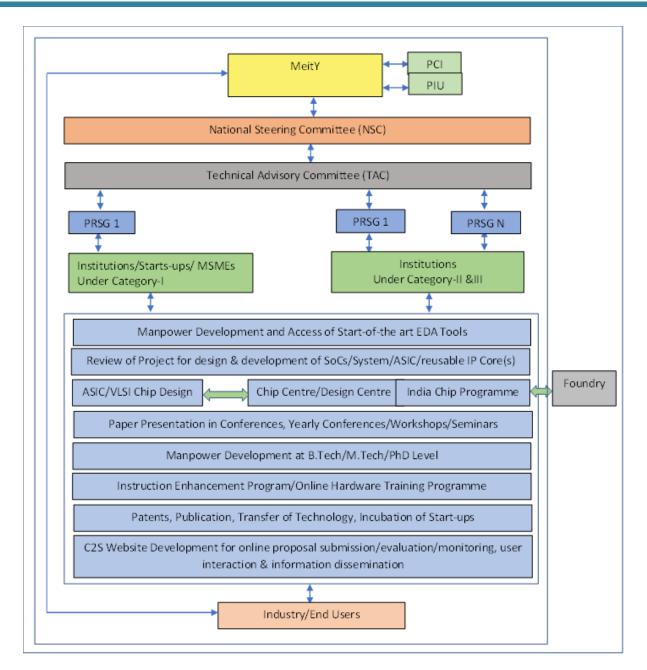

To fulfil the vision and mission of NPE-2019, there is a fundamental need to create highly skilled and trained manpower in the areas of hardware IPs design, IC design, SoC design, System design and applications. The proposed **"Chips to Startup (C2S)"** Programme addresses each entity of the value chain in Electronics System Design viz. quality manpower training, research and development, hardware IPs design, System design, application-oriented R&D, Prototype design and deployment with the help of Academia, Industry, Start-ups and R&D establishments.

**Stakeholder's Consultation:** The contours of the proposed C2S Programme has been evolved by following an extensive stakeholder consultation process (involving a number of brainstorming sessions with experts from 60 SMDP-C2SD Participating Institutions, Government organizations, Industry and Industry Association). TAC (Technical Advisory Committee) under the Chairmanship of Prof. Dinesh Kumar Sharma, IIT Bombay while reviewing the progress of present phase of SMDP (viz. SMDP-C2SD) in its 6<sup>th</sup> meeting, also provided guidance on firming-up the proposal on next phase of SMDP (viz. C2S).

**Recommendation by NSC (National Steering Committee)**: Based on the details presented to NSC in its 5<sup>th</sup> meeting, NSC under the Chairmanship of Secretary, MeitY, in-principally agreed for initiation of next phase of SMDP (viz. C2S) simultaneously with SMDP-C2SD programme.

**Impact Assessment by VLSI Society of India:** VLSI Society of India, while carrying out impact assessment of SMDP-C2SD Programme, not only noted its successful implementation but also recommended that the next Phase of SMDP should aim to broaden the VLSI design base by including more number of institutions and facilitate industry-led R&D by way of implementing more collaborative projects with industry targeting import substitution and commercialization. Efforts should be made to make available the facilities provided by the Chip Centre (including the design infrastructure support) in centralized manner, accessible to participating institutions across the country.